上海微系统所在三维垂直型存储器设计领域取得重要进展

近日,中国科学院上海微系统与信息技术研究所相变存储器课题组针对三维垂直型存储器,从理论上总结了芯片速度受限的原因和偏置方法的相关影响,提出了新型的偏置方法和核心电路,相关成果以研究长文的形式发表在2018年7月的国际超大规模集成电路顶级期刊IEEE Transactions on Very Large Scale Integration (VLSI) Systems [vol. 26, no. 7, pp. 1268-1276] 上。审稿人认为,该论文首次将动态仿真应用于三维垂直型存储器。

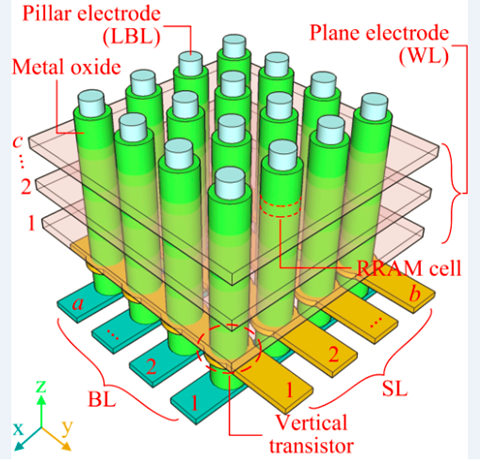

三维集成电路是维持集成电路产业高速发展的关键,而三维存储器更是三维集成技术中的领跑者。三维新型非易失存储器因其独特的速度、密度和寿命优势,被寄予革新现有计算架构的厚望,是国际上的竞争焦点。作为三维新型非易失存储器的两种主流阵列结构之一,当前三维垂直型阵列结构的研究主要集中在器件和阵列层面。但是,三维存储器在垂直方向的集成、新型偏置方法和新的存储器件影响了芯片的速度和可靠性,给三维存储器的芯片设计方法学带来了重大挑战。

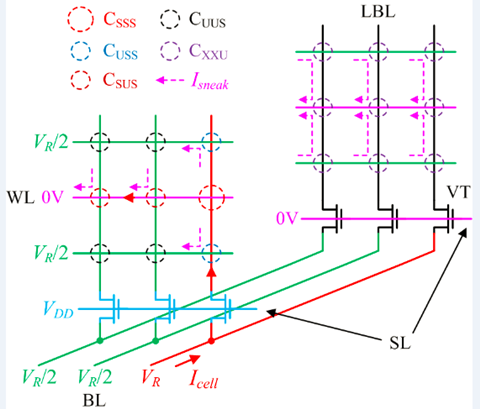

针对这一重大挑战,中国科学院上海微系统与信息技术研究所雷宇等人首先提出三维垂直型存储器新型偏置方法,与传统偏置方法相比,新型偏置方法支持子阵列中的单个比特读取,降低了功耗,提高了读写速度,提高了读正确率;根据新型偏置方法设计了芯片阵列核心电路;分析了影响芯片读出操作的主要因素;提出变化参考与寄生匹配读出电路,该电路读取速度快,读取正确率高,可适用于各种类型、不同容量的三维垂直型存储器;实验结果表明:提出的读出电路随机读取时间比传统方法缩短了75%,典型和最差电阻时的误读取数量与传统方法相比分别减少了100%和95.31%。

该论文在国际上首次归纳和分析了影响三维垂直型存储器读出操作的主要因素,提出了三维垂直型新型存储器的首个集成电路设计,也是是世界上首篇关于三维垂直型新型存储器集成电路设计的论文。研究成果为三维垂直型存储器的工程实现提供了技术参考,并推动了三维存储器芯片设计方法学的进步。研究工作得到了审稿人的高度评价:“提出了关于三维垂直型存储器电路引人入胜、新颖的观点和构思”(“interesting novel points and ideas regarding 3D circuits”),“重要的实际意义”(“practical significance”),“完整而令人信服的结果”(“The concept is new for 3D NVMs and the results are sound”),“首次将动态仿真应用于三维垂直型新型NVM(之前大部分使用静态分析)”(“this is the first time I see dynamic simulations (previous publications are mostly related to static analysis)”)。

上海微系统所雷宇博士为论文的第一作者,研究工作在宋志棠研究员的领导下展开。研究工作得到了中国科学院战略性先导科技专项、国家集成电路重大专项、国家自然科学基金、上海市科委等支持。

IEEE Transactions on Very Large Scale Integration (VLSI) Systems (《IEEE超大规模集成系统汇刊》)是国际超大规模集成电路和存储器设计的顶级期刊,由IEEE电路与系统协会、IEEE计算机协会和IEEE固态电路协会共同出版;期刊为月刊,其7月刊只收录了18篇论文;自1993年创刊以来,共发表论文近5000篇,中国内地共发表100余篇。

论文链接:https://ieeexplore.ieee.org/document/8327898/

DOI: 10.1109/TVLSI.2018.2816246

三维垂直型存储器阵列结构

提出的偏置方法及相关分析