上海微系统所在三维存储器设计领域取得重要进展

近日,中国科学院上海微系统与信息技术研究所相变存储器课题组在三维存储器设计领域取得重要进展,相关成果以"A Single-Reference Parasitic-Matching Sensing Circuit for 3-D Cross Point PCM"为题,发表在国际集成电路重要期刊(前六位)IEEE Transactions on Circuits and Systems II: Express Briefs [vol. PP, no. 99, 2017]上。这是世界上首篇关于三维相变存储器读出电路设计的文章,也是SCI刊物三维相变存储器电路设计发表的首篇文章。

相变存储器利用电脉冲诱导存储材料在非晶态与晶态之间切换,具有非挥发性、循环寿命长、写入速度快、稳定性好、功耗低等优点,被业界认为是下一代存储技术的最佳解决方案之一。

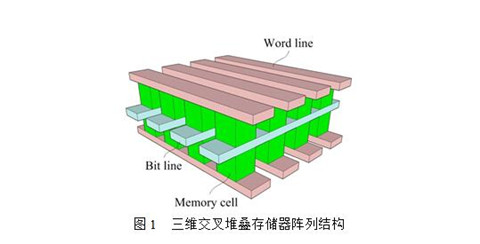

三维集成技术通过芯片或器件在垂直方向的堆叠,可以显著增加芯片集成度,是延续摩尔定律的一种重要技术。其中,一种交叉堆叠(cross point)的三维存储结构被广泛应用于非易失存储器。

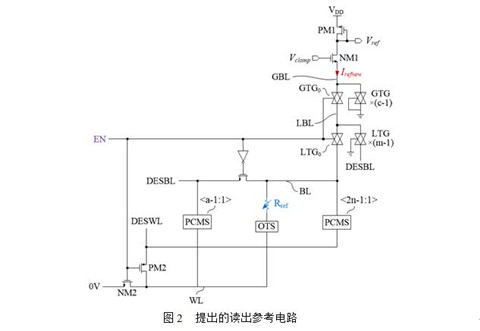

当前,三维新型非易失存储器的研究主要集中在器件和阵列层面。与传统的二维存储器不同,三维相变存储器采用了新型的双向阈值开关(Ovonic Threshold Switch,OTS)器件作为选通器件(selector)。根据OTS器件的物理特性和三维交叉堆叠阵列结构的特点,三维交叉堆叠型相变存储器采用一种V/2偏置方法以实现存储单元的操作。但V/2偏置方法和OTS器件导致阵列中诸多未被选择的存储单元的漏电。漏电导致读出电路读取正确率和读出速度的下降。存储器在进行读操作时,阵列中的寄生器件会降低读取速度。二维存储器中,这些器件主要集中在平面方向;但在三维存储器中,垂直方向的寄生器件会进一步降低读取速度。因此,对于影响三维存储器读操作各因素的量化分析和提高其速度的集成电路设计是必要的。

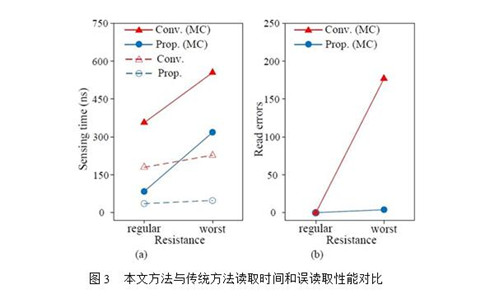

三维相变存储器的具体工程细节属商业机密,可参考资料较少。中国科学院上海微系统与信息技术研究所雷宇等人首先设计了三维相变存储器的阵列核心电路,再对三维相变存储器的读路径进行了分析,最终总结了影响三维相变存储器读操作的五种因素。这五种因素与三维存储器阵列参数的量化关系也被指出。以此为基础,论文提出了一种适用于三维存储器的单参考和寄生匹配读出电路。该电路采用变化参考电流,并对以上五种因素在读方向和参考方向进行了匹配。实验结果表明,读出时间比传统方法缩短了79%,误读取个数下降了97%。

论文提出的读出电路还可适用于其它三维交叉堆叠型非易失存储器。并因读出电路与阵列的设计参数直接相关,相关设计人员可根据其存储器的容量,方便的设计出适用于不同容量存储器的、高性能的读出电路。

该论文在国际上首次归纳分析了对三维交叉堆叠型存储器读操作有影响的五种因素,提出了第一种与三维新型非易失存储器阵列特性相关的读出电路,也是世界上首篇关于三维相变存储器读出设计的文章。

中国科学院上海微系统与信息技术研究所信息功能材料国家重点实验室是论文的第一单位,中国科学院大学是论文的第二单位。上海微系统所博士生雷宇为论文的第一作者,陈后鹏研究员为论文通讯作者,研究工作在宋志棠研究员的领导下展开。论文于2016年12月投出。该研究工作得到了中国科学院战略性先导科技专项、国家集成电路重大专项、国家自然科学基金、上海市科委等支持。

论文链接:http://ieeexplore.ieee.org/document/7987059/ DOI: 10.1109/TCSII.2017.2729665