上海微系统所在纳米级真空沟道器件的大规模制备技术方面取得进展

真空沟道电子器件采用真空缝隙作为器件沟道,其电子迁移率优于所有半导体器件,可满足高频通信、高保真模拟电路以及在高温、强辐射等极端环境下的应用需求。近年来,真空沟道电子器件成为后摩尔基础元器件的研究热点。然而,现有真空沟道电子器件多采用电子束光刻、离子束聚焦刻蚀等方法加工其纳米沟道,与 CMOS 工艺兼容性差,难以实现大规模制备和应用。

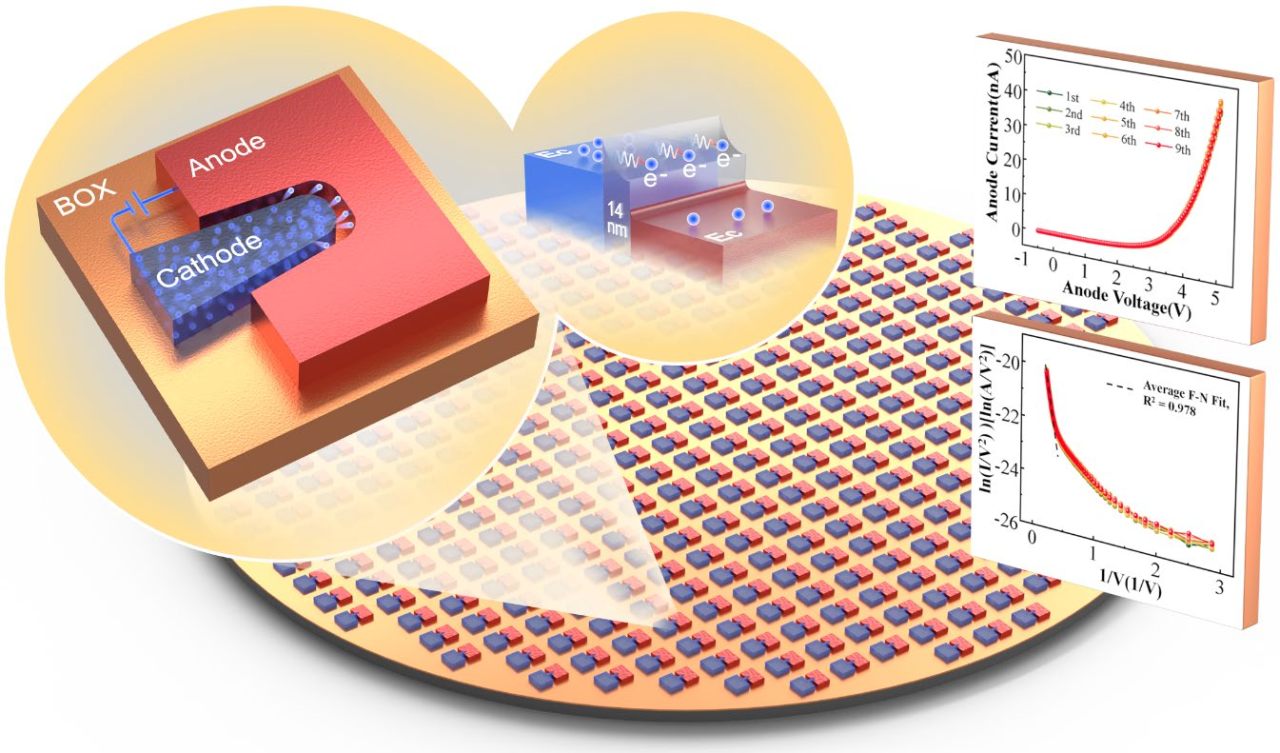

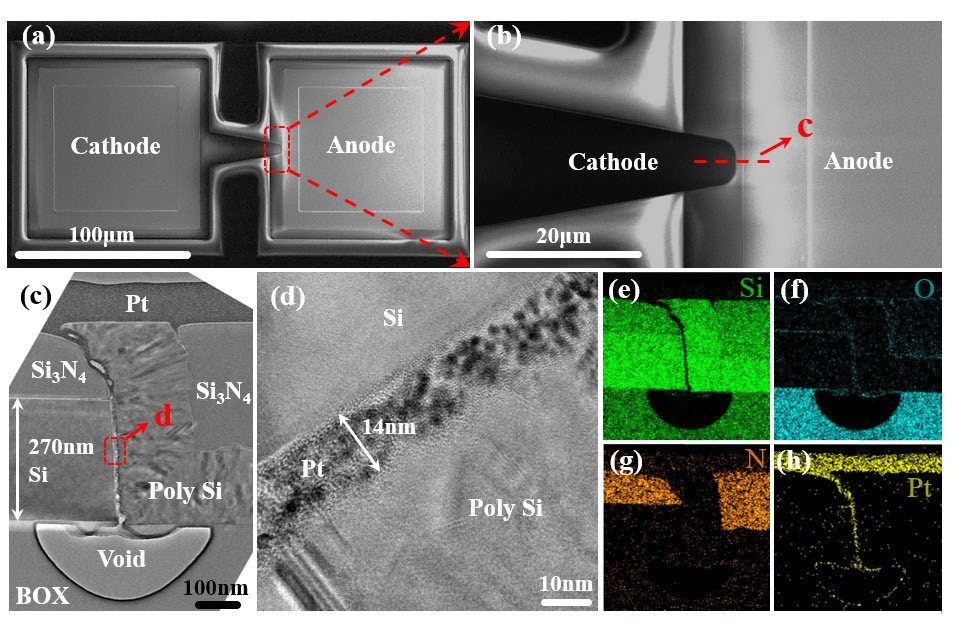

近日,中国科学院上海微系统与信息技术研究所集成电路材料全国重点实验室俞文杰课题组提出了一种结合化学机械抛光(CMP)及选择性湿法腐蚀性的新型真空沟道电子器件集成方案。基于SOI衬底材料,该研究团队成功制备了具有14 nm真空沟道的原型器件,该器件实现了较低开启电压(1.8 V)和较高发射电流(70nA@5V,T=300K)。本工作还综合分析了器件的时间稳定性、温度响应特性等。该方案与 CMOS 工艺完全兼容,其具有工艺简单、可控性高、可拓展性强等优势,对真空沟道电子器件的大规模制造有重要的参考意义。

相关论文以 “ A Novel Approach for Large-Scale Fabrication of Nanoscale Vacuum Electronic Devices with High Compatibility and Controllability”为题,以编辑精选文章(Editors’ Picks)发表于电子器件领域权威期刊《 IEEE Electron Device Letters》。中国科学院上海微系统所博士研究生陈锦和刘强助理研究员为该论文共同第一作者,刘强助理研究员和俞文杰研究员为该论文通讯作者。相关工作得到国家自然科学基金青年科学基金项目(C 类) [原青年科学基金项目]、上海市启明星扬帆计划等项目资金支持。

论文链接:https://ieeexplore.ieee.org/document/11037418

图 1 真空沟道电子器件示意图及其电子发射性能

图 2 真空沟道电子器件微纳结构