上海微系统所在超导EDA算法研究方面取得重要进展

文章来源: | 发布时间:2023-09-28

文章来源: | 发布时间:2023-09-28 | 【打印】 【关闭】

最近,中国科学院上海微系统与信息技术研究所任洁研究员团队在超导集成电路电子设计自动化技术(EDA)研究领域取得了重要进展。研究团队提出了一种基于大规模有限状态机(FSM)分解的超导单磁通量子(SFQ)逻辑时序电路综合方法,利用超导SFQ逻辑门自身的特性与优势提升SFQ时序电路的性能,相关成果于2023年10月以题为“Sequential Circuits Synthesis for Rapid Single Flux Quantum Logic Based on Finite State Machine Decomposition”的学术论文发表在中国计算机学会推荐的A类期刊IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems上(https://doi.org/10.1109/TCAD.2023.3245542)。此外,研究团队还开发了针对约瑟夫森结器件的模拟仿真器JSICsim,该仿真器集成了新型约瑟夫森结RCLSJ模型,并支持大规模约瑟夫森结电路的并行仿真,仿真速度相较同类产品最多可提升47倍,相关成果已于2023年3月以题为“JSICsim - An Analog Simulator for Superconductor Integrated Circuit”的学术论文发表在IEEE电路与系统协会老牌旗舰期刊之一IEEE Transactions on Circuits and Systems II: Brief Express期刊上(https://doi.org/10.1109/TCSII.2022.3215912)。

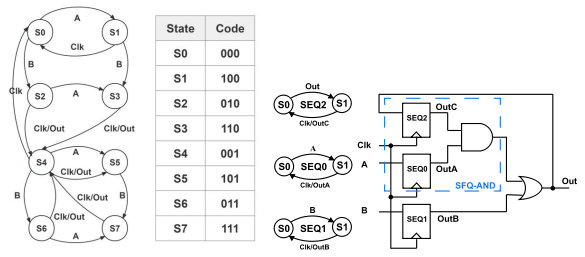

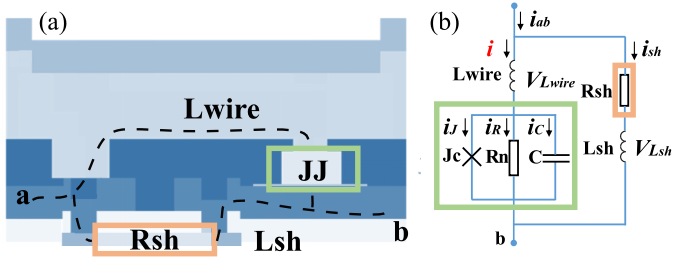

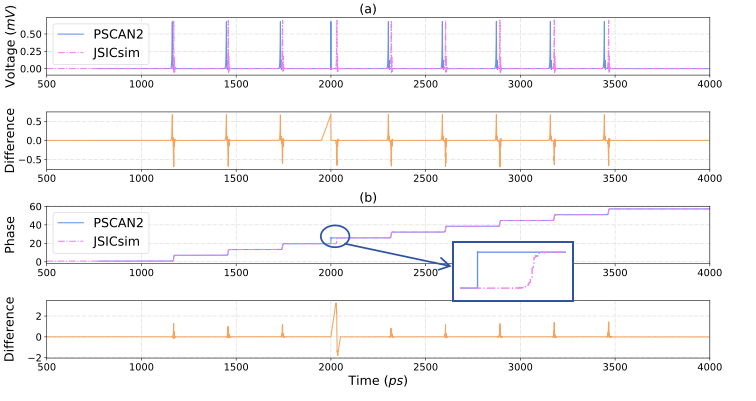

EDA技术是芯片设计的核心技术,高效的EDA算法能够提高芯片设计的性能和稳定性,并缩短设计迭代周期,是集成电路领域的研究热点。在EDA技术中时序逻辑综合工具方面,由于SFQ逻辑的门级流水线特性,传统的CMOS时序逻辑综合算法难以兼容超导SFQ时序电路设计,使超导SFQ芯片的自动化设计受限。为了解决这一问题,研究团队基于SFQ逻辑门的特点提出了一种将大规模超导SFQ时序电路状态机分解为元状态机,并将元状态机进行SFQ逻辑映射的方法。相较于其他SFQ时序电路综合方法,使用该基于有限状态机分解的方法能够将电路综合后网表的面积最多减少70%,并使生成的电路结构兼容SFQ门级流水线结构,为超导SFQ数字电路的自动化设计提供了重要的理论和算法基础。在EDA技术中的电路模拟仿真领域,高速高精度的模拟仿真器是分析超导电路功能、提高设计-工艺关联性、验证数字仿真可靠性的关键工具。长期以来,超导约瑟夫森结模拟仿真主要使用开源工具PSCAN2,其仿真速度与精度均无法达到大规模超导芯片的设计需求。为了掌握自主可控的模拟仿真器技术,提高其仿真速度和精度,研究团队研发了并行模拟仿真器架构以降低大规模电路仿真所需的时间开销,并提出了新型的RCLSJ模型以实现更加精确的约瑟夫森结行为描述。JSICsim相较于PSCAN2可将仿真耗时降低一个数量级,并且使千万约瑟夫森结级大规模超导电路仿真成为可能。

上海微系统所博士研究生杨树澄为两项工作的第一作者,任洁研究员为通讯作者。上述研究工作获得中科院先导专项、国家自然基金、国家重点研发计划项目、上海科技委项目等支持。

论文原文链接:

https://doi.org/10.1109/TCAD.2023.3245542

https://doi.org/10.1109/TCSII.2022.3215912

图1:测试电路有限状态机及其分解、匹配结果

图2:逻辑综合后的2bit计数器波形对比。左图使用参考文献中的方法,右图使用基于状态机分解的方法。

图3:JSICsim中的RCLSJ模型

图4:JSICsim与PSCAN2仿真波形对比